-

quartusii9 0下载

大小:2.19 GB系统:Win7/8/10 类别:杂类软件语言:简体中文 时间:2020-04-10 11:51:47

quartusii9 0 是由altera公司推出的一款专业PLD软件开发平台,新版本拥有全新的操作界面和功能,包括设计英特尔FPGA、片上系统和CPLD所需的一切,带来了全新的功能和全新的优化引擎,增加了Spectra-Q引擎,可以有效地提升工作效率。可以通过引用子系统和 IP 元件的仿真信息来生成分层仿真脚本,而不需要遍历系统层次结构。

1、支持软件源文件的添加和创建,并将它们链接起来生成编程文件;

2、定时/时序分析与关键路径延时分析;

3、可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;

4、quartus ii 9.0破解版提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:

5、自动定位编译错误;

6、能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件。

7、功能强大的逻辑综合工具;

8、可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

9、完备的电路功能仿真与时序逻辑仿真工具;

10、高效的期间编程与验证工具;

11、芯片(电路)平面布局连线编辑;

12、LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;

13、可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件;

14、使用组合编译方式可一次完成整体设计流程;

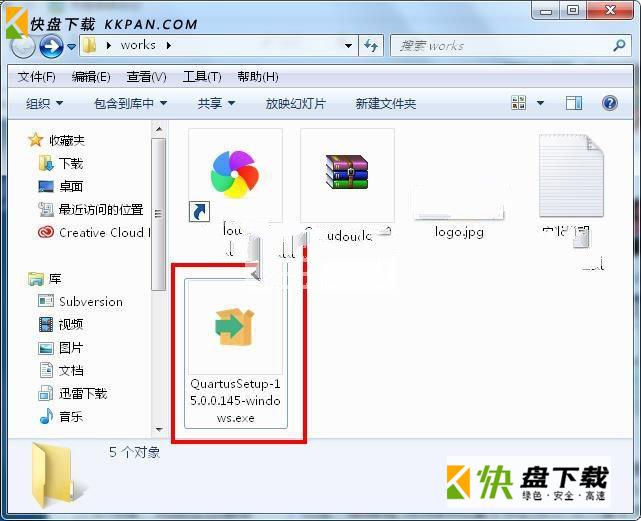

1、下载完毕解压缩,然后运行我们的安装程序。

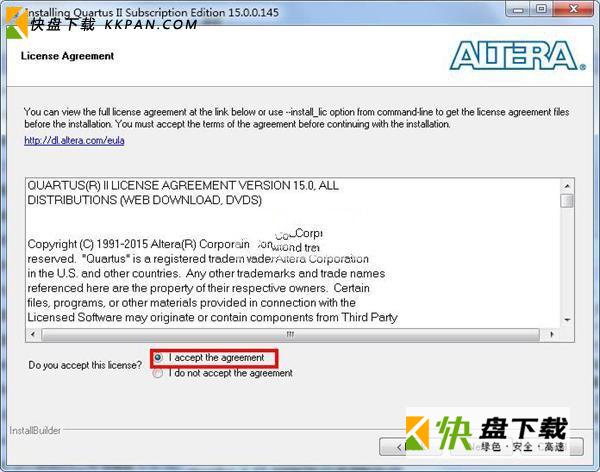

2、点击next,然后选择接受协议,再点击next。

3、选择安装路径,软件比较大,建议安装在磁盘空间比较大的盘符。

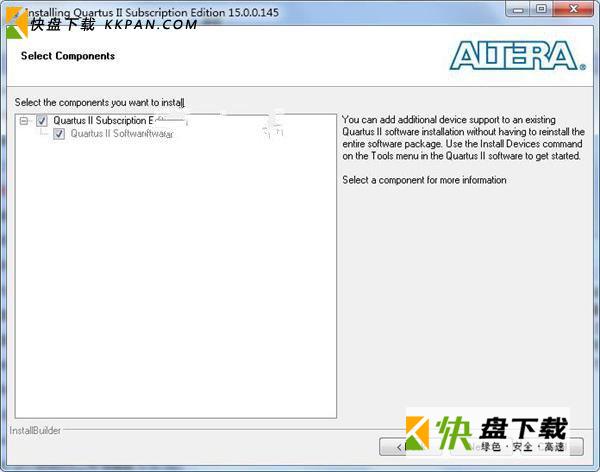

4、选择安装组件,只有我们的软件一个,不过需要将近6G的空间。

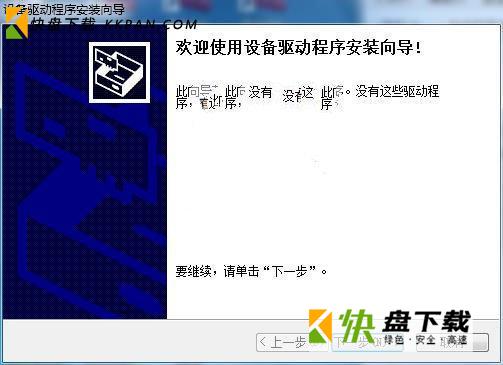

5、然后就是一直点击下一步安装了,安装完成弹出驱动程序安装,点击下一步安装驱动程序。

一、多功能管脚的设置

在用flash分配完管脚后编译出现如下错误:

Error: Can’t place multiple pins assigned to pin location Pin_108 (IOC_X34_Y2_N0)

nfo: Fitter preparation operations ending: elapsed time is 00:00:00

Error: Can‘t fit design in device

Error: Quartus II Fitter was unsuccessful. 2 errors, 0 warnings

Error: Quartus II Full Compilation was unsuccessful. 4 errors, 56 warnings

原因是不能分配给多功能管脚PIN_108。

这是由于PIN_108是一个多功能管脚,还有一个功能是nCEO,也是默认的功能。如果要用它当普通IO,需要提前设置一下:assignments》device》device and pin options》dual-purpose pins里面把nCEO设置成use as regular i/o就可以了。

二、仿真时存储器初始化

在使用FPGA内部的RAM时,会有一个初始化文件.mif,给RAM加上初始值或当作ROM用,因此仿真时必须把相应数据导入,首先要把mif文件转换为.hex文件或.rif文件。

在Quartus II环境下,打开mif文件,点Save As,选择Hexadecimal(Intel-Format) File(*.hex),或者点击Export,用Save as type选择RAM Initialization File (*.rif),也可能在命令行下输入:

mif2rif

打开ram模块文件,找到lpm_file或init_file,指向刚刚生成的hex文件或rif文件。

lpm_ram_dp_component.lpm_file = “path

使用hex文件时,不需要compiler directives,使用rif文件时,需要加入USE_RIF,如下

vlog -work alter_mf altera_mf.v +define+USE_RIF=1

这样就完成了数据导入。

三、多模块或多进程驱动同一信号

Error (10028): Can‘t resolve multiple constant drivers for net “FLASH_A[7]” at led.v(32)

用Verilog描述电路时,一个信号只能在一个进程中驱动,如果在多个进程中对其驱动的话将产生如上错误。解决方法为可以另加一个信号,通过在另一个进程中监视这个信号做出相应的动作

Flash组件损坏修复工具10953人在玩看视频的时候经常会遇到提示Flash组件损坏,必要的系统组件未能正常运行,请修复Adobe Flash Player导致无法正常观看视频,FlashRepairTool工具是Flash官方出的一款修改工具,可以有效的修改Flash组件损坏问题。

下载

MATLAB 2019b破解版下载3885人在玩MATLAB R2019b中文破解版是由mathworks公司推出的一款专业商业数学软件,这个是MATLAB R2019a的升级版本,兼容windows 64位操作系统,软件允许矩阵操作,函数和数据绘图。

下载

今日制造破解版下载2678人在玩今日制造是迈迪信息技术有限公司倾情打造的一款以PDM功能和云资料管理为核心亮点打造的一款轻量化三维设计工具,简洁清爽的UI风格,丰富的三维设计工具,海量资源模型,简单易用的PDM

下载

ET服装CAD下载2067人在玩ET服装CAD软件是一款专业的服装CAD设计软件,它这服装的设计方面相当的全面,还拥有逼真的模型制作,也支持对模块的套用、帮助用户快速的完成服装的设计制作。

下载

SPSS Clementine 19破解版1556人在玩Statistical Product and Service Solutions,中文名统计产品与服务解决方案软件,是一款老牌的数据统计软件。它拥有图表分析、数据管理、输出管理、统计分析等等众多功能,而它的统计分析包括回归分析、数据简化、描述性统计、生存分析、相关分析等等非常多方面的分析。

下载

无忧隐藏(文件隐藏工具)下载1276人在玩无忧隐藏是一款便捷快速的的进程隐藏工具,通过该软件,用户可以将自己的文件,下载程序,图标、软件等进行隐藏,还支持快速锁定屏幕、窗口透明度、自动隐藏并运行指定任务等功能。

下载

Proteus Professional破解版下载1217人在玩Proteus Professional 8.9是proteus8.8的升级版本,这是一款专业强大好用的系统仿真开发软件,软件提供了丰富的模块和人性化的工作流程,实现了从原理图设计、单片机编程、系统仿真到PCB设计,真正实现了从概念到产品

下载

piano钢琴模拟器破解版下载1068人在玩synthesia piano破解版是一款好用的钢琴模拟器软件,有了这款工具就可以把你的键盘变成虚拟的键盘按键了,支持midi和midi键盘输入,同时还可以与各类设备连接进行弹奏,软件还内置了丰富的曲库,用户不需要懂五线谱就可以弹奏出美妙的乐章。

下载

solidworks2016破解版下载1044人在玩solidworks2016破解版是一款一体化的机械设计解决方案,它软件功能强大,组件繁多,对于熟悉Windows用户来说操作更加简便,可以完美地制作出复杂的零件模型。

下载

文泰刻绘下载1033人在玩文泰刻绘是一款好用的全方位数控设备完美解决方案,让我们可以完全免费使用该软。能够完成用户刻字绘图的全部需要。

下载